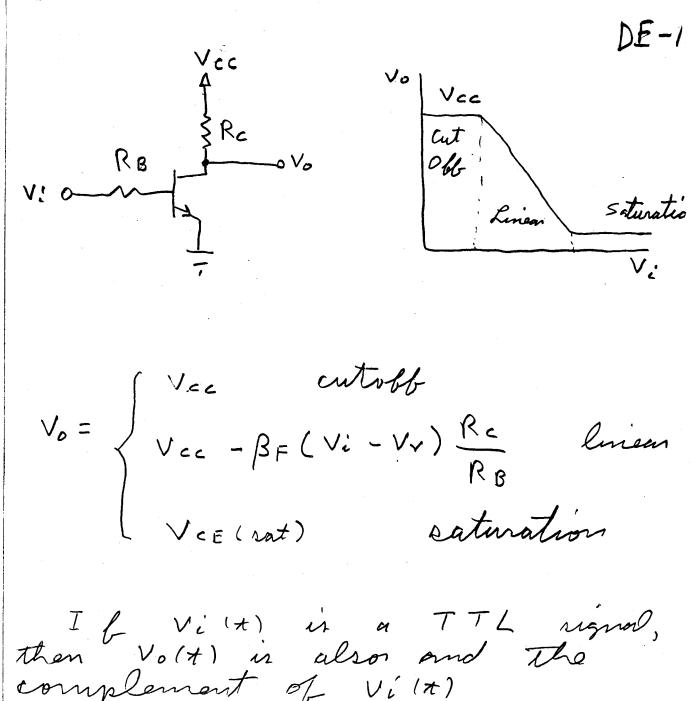

complement of Vi(x)

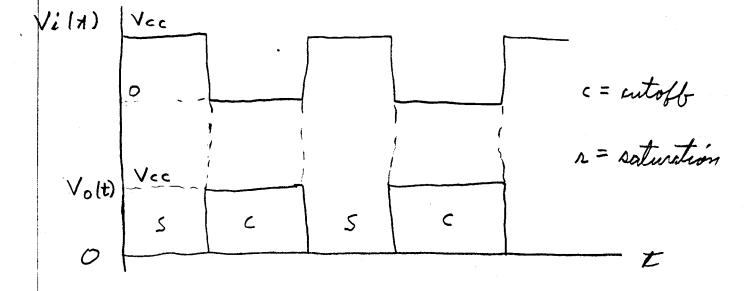

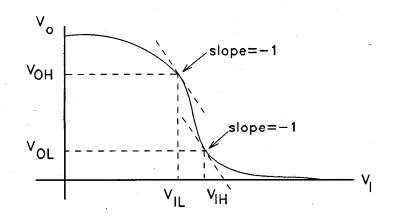

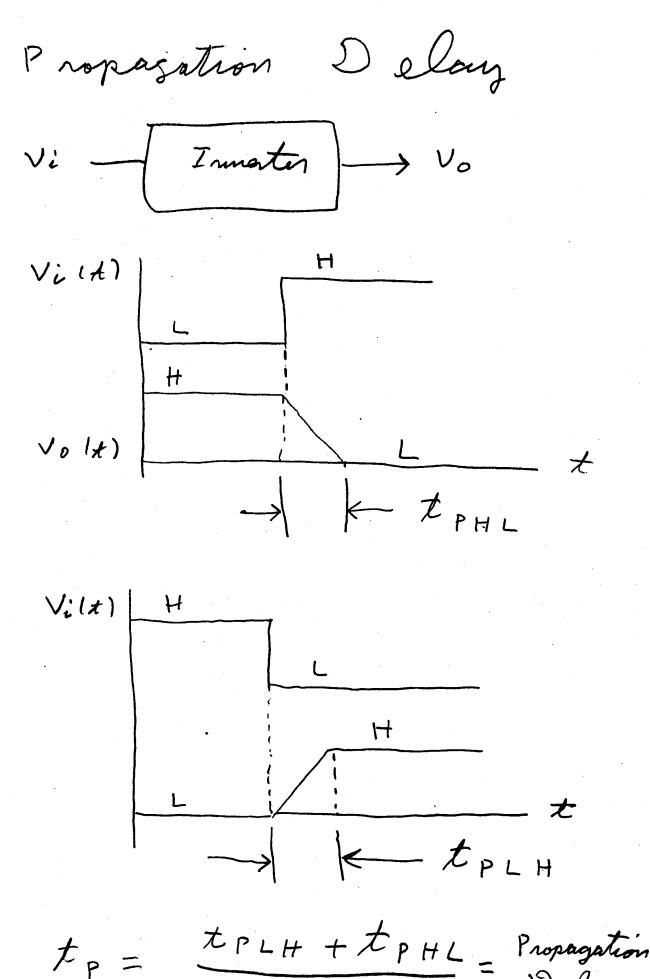

Tow Noise Margin N M. L = VIL - VOL

High Noise Margin N M H = VOH - VIH

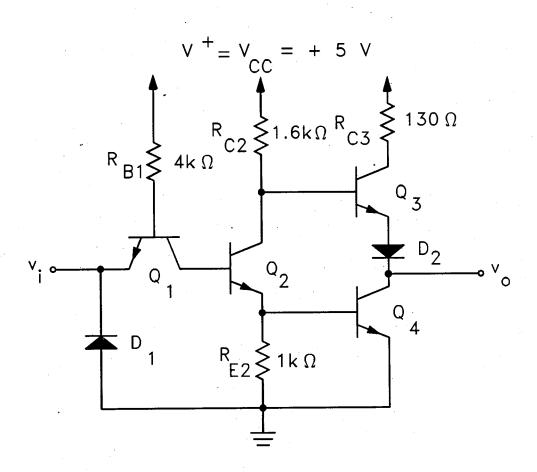

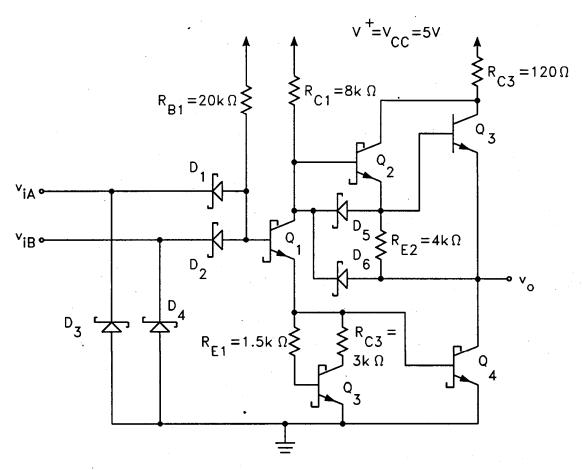

Figure 8-10 7404 TTL INVERTER.

Standond TTL Innerter

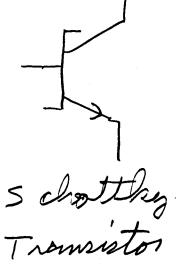

Schotthy Diodo

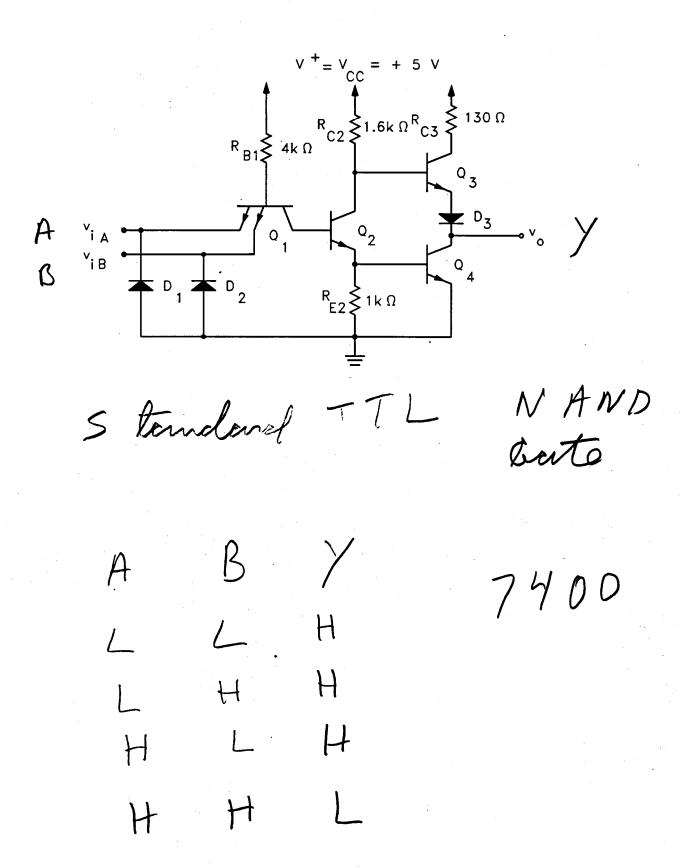

74 L S 0 0

NAND bato

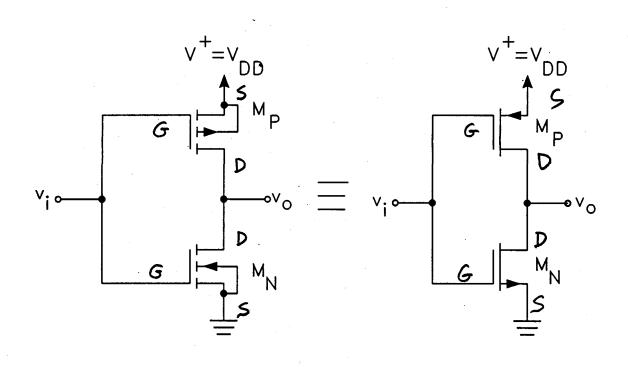

C MOS INVERTER For N Channel Enhancement Moolo Morket if VGS > VTO D To S a short, below open For P Chennel Enhancement Mode Morbet if VSG > IVTOl a short, below open | VGS | > | VTO | D to 5 is a short

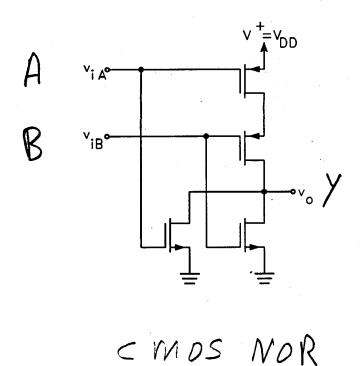

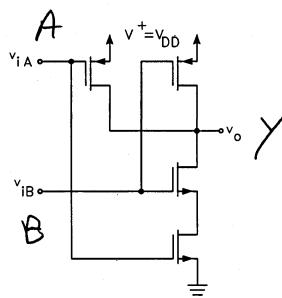

ABY LLHL HHLL H ABX LHHH HHLH HHL

CMOS NAND

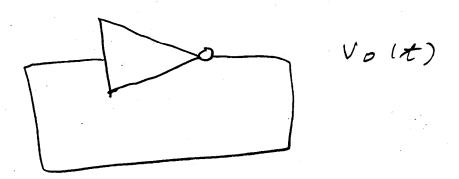

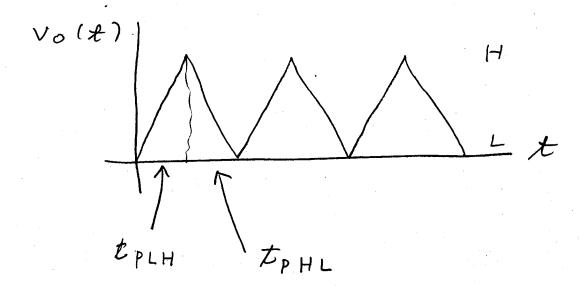

Ring Oscillatos I merter

$$T = t_{PLH} + t_{PHL} = 2 t_{P}$$

$f_{o} = \frac{1}{T} = \frac{1}{2 t_{P}}$

If N innerters are cascaded

$T = N(t_{PLH} + t_{PHL})$

$t_{p} = \frac{1}{2N t_{o}}$

N has to be odd

# Georgia Institute of Technology

## School of Electrical and Computer Engineering

| ECE 3042   | Microele       | Microelectronic Circuits Laboratory |                     |        | Verification Sheet |  |  |

|------------|----------------|-------------------------------------|---------------------|--------|--------------------|--|--|

|            |                |                                     |                     |        |                    |  |  |

| NAME:      |                |                                     | SECTION:            |        |                    |  |  |

| GT NUMBER: |                |                                     | GTID:               |        | <u>-</u>           |  |  |

|            | Experim        | ent 8: Digital Electror             | nic Circuits        |        |                    |  |  |

| Drocoduro  | Time Completed | Data Camplated                      | Varification / Must | Doints | Doints             |  |  |

| Procedure        | Time Completed | Date Completed | Verification (Must | Points   | Points   |

|------------------|----------------|----------------|--------------------|----------|----------|

|                  |                |                | demonstrate        | Possible | Received |

|                  |                |                | circuit)           |          |          |

| 2. BJT Inverter  |                |                |                    | 25       |          |

|                  |                |                |                    |          |          |

| 3. Standard TTL  |                |                |                    | 25       |          |

| Inverter         |                |                |                    |          |          |

| 4. 74LS TTL      |                |                |                    | 25       |          |

| Inverter         |                |                |                    |          |          |

| 5. CMOS Inverter |                |                |                    | 25       |          |

|                  |                |                |                    |          |          |

To be permitted to complete the experiment during the open lab hours, you must complete at least **three** procedures during your scheduled lab period or spend your entire scheduled lab session attempting to do so. A signature below by your lab instructor, Dr. Brewer, or Dr. Robinson permits you to attend the open lab hours to complete the experiment and receive full credit on the report. Without this signature, you may use the open lab to perform the experiment at a 50% penalty.

| SIGNATURE: | DATE: |

|------------|-------|

|            |       |

### **ECE 3042 Check-off Requirements for Experiment 8**

Make sure you have made all required measurements before requesting a check-off. For all check-offs, you must demonstrate the circuit or measurement to a lab instructor. All screen captures must have a time/date stamp.

#### 2. BJT Inverter

- ✓ Screen capture of output voltage versus input voltage for  $Z_L = \infty$ . Adjust x & y scales so that plot uses most of the scope screen.

- ✓ Measurement of VIL, VIH, VOL, VOH, NML, and NMH with scope cursors. Reference Fig. 8.7 and Eqns. 8.1 & 8.2.

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$ . Measurement of rise time, fall time, and storage time with scope cursors.

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$  and 300pF cap across  $R_B$ . Measurement of rise time, fall time, and storage time with scope cursors.

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$  and diode from base to collector. Measurement of rise time, fall time, and storage time with scope cursors.

#### 3. Standard TTL Inverter

- ✓ Screen capture of output voltage versus input voltage for  $Z_L = \infty$ . Adjust x & y scales so that plot uses most of the scope screen.

- ✓ Measurement of VIL, VIH, VOL, VOH, NML, and NMH with scope cursors. Reference Fig. 8.7 and Eqns. 8.1 & 8.2.

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$ .

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and voltage at collector of Q3.

- ✓ Previous two requirements repeated for *f* changed to 1MHz.

#### 4. 74LS TTL Inverter

- ✓ Screen capture of output voltage versus input voltage for  $Z_L = \infty$ . Adjust x & y scales so that plot uses most of the scope screen.

- ✓ Measurement of VIL, VIH, VOL, VOH, NML, and NMH with scope cursors. Reference Fig. 8.7 and Eqns. 8.1 & 8.2.

- ✓ Screen capture of 100kHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$ .

- ✓ Screen capture of 1MHz 5 Vpp 2.5V dc square wave input and output voltage for  $Z_L = \infty$ .

- ✓ Measurement of average power dissipation per gate for no input, 100kHz 5 Vpp 2.5V dc square wave input, and 1MHz 5 Vpp 2.5V dc square wave input.

- ✓ Measurement of ring oscillator frequency and calculation of propagation delay  $t_p$ . Measurement of power dissipation  $P_D$  of ring oscillator. Calculation of  $t_p P_D$ .

#### 5. CMOS Inverter

- ✓ Screen capture of output voltage versus input voltage for  $Z_L = \infty$ . Adjust x & y scales so that plot uses most of the scope screen.

- ✓ Measurement of VIL, VIH, VOL, VOH, NML, and NMH with scope cursors. Reference Fig. 8.7 and Eqns. 8.1 & 8.2.

- ✓ Screen capture of 100kHz 10 Vpp 5V dc square wave input and output voltage for  $Z_L = \infty$ .

- ✓ Screen capture of 100kHz 10 Vpp 5V dc square wave input and output voltage for 1nF load cap.

- ✓ Measurement of average power dissipation per gate for both a 100kHz 10 Vpp 5V dc square wave input and a 15MHz 10 Vpp 5V dc square wave input.

- ✓ Measurement of ring oscillator frequency and calculation of propagation delay  $t_p$ . Measurement of power dissipation  $P_D$  of ring oscillator. Calculation of  $t_p P_D$ .